隨著無線通信技術(shù)的飛速發(fā)展,射頻集成電路(RFIC)作為連接數(shù)字世界與無線信號的關(guān)鍵橋梁,其設(shè)計復(fù)雜性日益增加。從智能手機到物聯(lián)網(wǎng)設(shè)備,從5G基站到衛(wèi)星通信,RFIC的性能直接決定了整個系統(tǒng)的通信質(zhì)量、功耗與成本。射頻電路的工作頻率高、信號微弱、對外界干擾敏感,設(shè)計過程充滿了挑戰(zhàn)。本文將深入解析射頻集成電路設(shè)計中的常見核心問題,并提供相應(yīng)的解決思路與方案。

一、 常見問題剖析

- 噪聲與靈敏度問題

- 問題描述:射頻接收機需要處理極其微弱的信號(可達(dá)微伏級)。放大器、混頻器等有源器件內(nèi)部產(chǎn)生的噪聲,會淹沒有用信號,導(dǎo)致接收靈敏度下降,通信距離縮短或誤碼率升高。

- 核心指標(biāo):噪聲系數(shù)(NF)。

- 線性度與干擾問題

- 問題描述:在實際應(yīng)用中,強干擾信號(阻塞信號)或自身產(chǎn)生的諧波、交調(diào)產(chǎn)物會落入接收信道,造成信號失真。這要求電路具有良好的線性度,以處理大信號而不產(chǎn)生嚴(yán)重失真。

- 核心指標(biāo):輸入三階交調(diào)點(IIP3)、1dB壓縮點(P1dB)。

- 阻抗匹配與功率傳輸問題

- 問題描述:射頻信號在傳輸過程中,若源端、傳輸線、負(fù)載端的阻抗不匹配,會導(dǎo)致信號反射,造成功率傳輸效率下降、增益波動,甚至引起電路不穩(wěn)定(振蕩)。

- 核心指標(biāo):反射系數(shù)(Γ)、電壓駐波比(VSWR)、S參數(shù)(尤其是S11和S22)。

- 功耗與效率的平衡問題

- 問題描述:尤其在移動終端中,電池續(xù)航至關(guān)重要。功率放大器(PA)作為射頻前端最耗電的模塊,其效率直接決定整機功耗。但高效率(如開關(guān)類功放)和高線性度往往存在矛盾。

- 核心指標(biāo):功率附加效率(PAE)、整體系統(tǒng)功耗。

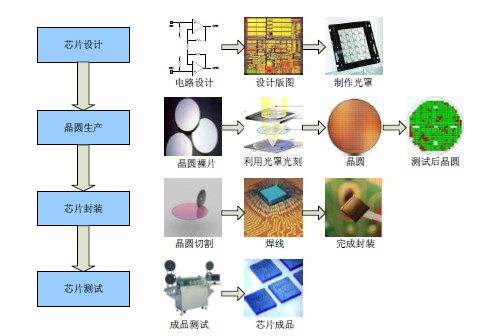

- 工藝變異與模型準(zhǔn)確性

- 問題描述:深亞微米CMOS工藝是RFIC的主流,但晶體管在高頻下的寄生效應(yīng)(如襯底損耗、柵極電阻)顯著,且工藝角(Process Corner)的波動會導(dǎo)致實際流片性能與仿真結(jié)果出現(xiàn)偏差。無源器件(電感、電容、傳輸線)的模型在高頻下也更為復(fù)雜。

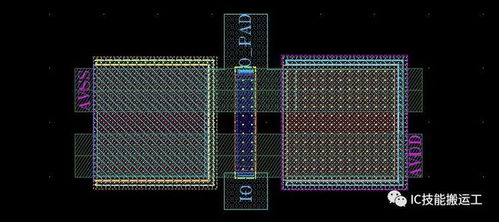

- 封裝與測試的寄生效應(yīng)

- 問題描述:封裝引線的電感和焊盤的電容會引入額外的寄生參數(shù),改變芯片內(nèi)部的射頻性能,可能導(dǎo)致頻率響應(yīng)偏移、增益下降或穩(wěn)定性問題。測試探針和PCB板同樣會引入誤差。

二、 關(guān)鍵解決方案與設(shè)計策略

- 優(yōu)化噪聲性能

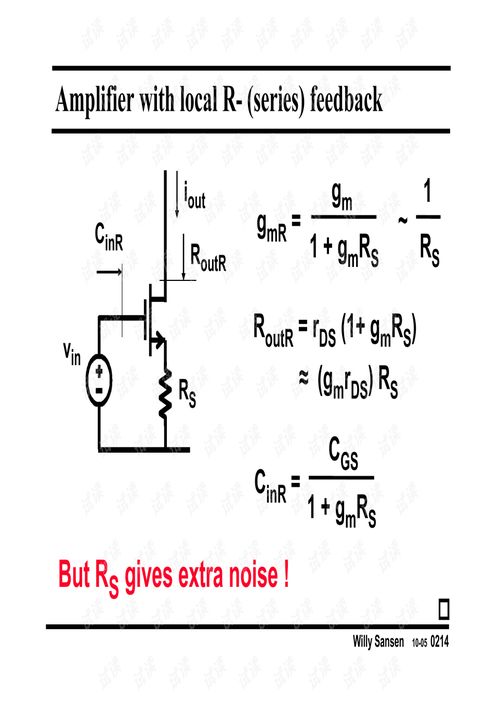

- 電路拓?fù)溥x擇:在低噪聲放大器(LNA)設(shè)計中,采用共源共柵(Cascode)結(jié)構(gòu)以平衡增益與噪聲;使用電感退化技術(shù)改善線性度和匹配。

- 器件尺寸與偏置優(yōu)化:通過仿真精細(xì)調(diào)整晶體管寬度、偏置電流/電壓,找到最小噪聲系數(shù)(NFmin)的最佳工作點。

- 阻抗匹配網(wǎng)絡(luò)設(shè)計:設(shè)計輸入匹配網(wǎng)絡(luò),使源阻抗呈現(xiàn)為晶體管獲得最小噪聲所需的最佳噪聲阻抗(Γopt),而非單純追求功率匹配(S11最小)。

- 提升線性度

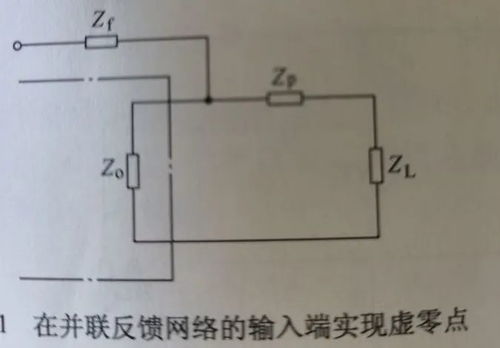

- 負(fù)反饋技術(shù):采用源極負(fù)反饋(電感或電阻)來提升線性度,但會犧牲一定增益和噪聲性能。

- 非線性補償技術(shù):如使用導(dǎo)數(shù)疊加(Derivative Superposition)等技術(shù),利用輔助晶體管抵消主晶體管的非線性電流。

- 前饋/預(yù)失真技術(shù):在功放等模塊中,通過檢測并注入反向失真信號來抵消非線性產(chǎn)物(更常用于板級或系統(tǒng)級)。

- 適當(dāng)選擇偏置點:工作在較高的偏置電流通常有利于線性度,但需與功耗權(quán)衡。

- 實現(xiàn)寬帶阻抗匹配

- 使用LC匹配網(wǎng)絡(luò):通過π型、T型或L型網(wǎng)絡(luò)進(jìn)行窄帶精確匹配。

- 寬帶匹配技術(shù):采用共源共柵結(jié)構(gòu)、負(fù)反饋(電阻反饋)或變壓器巴倫(Balun)來實現(xiàn)更寬頻帶的匹配,滿足多頻段/寬帶系統(tǒng)需求。

- 片上ESD保護電路的特殊設(shè)計:避免ESD結(jié)構(gòu)引入大的寄生電容破壞射頻端口的匹配。

- 管理功耗與效率

- 架構(gòu)創(chuàng)新:采用包絡(luò)跟蹤(ET)、平均功率跟蹤(APT)等先進(jìn)技術(shù),使功放的供電電壓隨輸入信號包絡(luò)動態(tài)調(diào)整,大幅提升平均效率。

- 開關(guān)類功放設(shè)計:研究E類、F類等開關(guān)模式功放,理論上可實現(xiàn)100%的效率,但需解決線性化和寬帶設(shè)計挑戰(zhàn)。

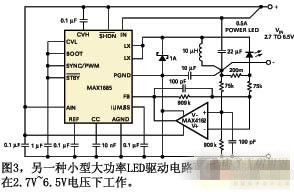

- 電源管理集成:在芯片內(nèi)集成高效的直流-直流轉(zhuǎn)換器(DC-DC),為功放提供可調(diào)電壓。

- 應(yīng)對工藝與模型挑戰(zhàn)

- 設(shè)計留有余量(Margin):在仿真時充分考慮工藝角、電壓、溫度(PVT)變化,確保在最壞情況下電路仍能滿足指標(biāo)。

- 采用穩(wěn)健設(shè)計:優(yōu)先選擇對工藝變化不敏感的電路結(jié)構(gòu)和器件尺寸。

- 可測試性設(shè)計(DFT)與微調(diào)(Trimming):在芯片中集成關(guān)鍵性能(如頻率、增益)的檢測電路和可調(diào)元件(如電容陣列),以便在測試或使用時進(jìn)行校準(zhǔn)。

- 抑制寄生與協(xié)同設(shè)計

- 芯片-封裝協(xié)同設(shè)計(CPC):在設(shè)計的早期階段就將封裝模型(包含鍵合線、焊球、封裝基板)納入整體仿真,優(yōu)化I/O布局和匹配網(wǎng)絡(luò)。

- 使用先進(jìn)封裝:采用倒裝芯片(Flip-Chip)、扇出型(Fan-Out)等封裝技術(shù),縮短互連長度,減少寄生電感。

- 片上隔離技術(shù):使用深N阱、保護環(huán)、隔離槽等技術(shù),減少襯底噪聲耦合和干擾。

****

射頻集成電路設(shè)計是一門需要深厚理論功底、豐富工程經(jīng)驗和不斷創(chuàng)新的藝術(shù)。面對噪聲、線性度、匹配、功耗等相互制約的挑戰(zhàn),設(shè)計師必須在復(fù)雜的多維參數(shù)空間中尋找最優(yōu)解。隨著工藝節(jié)點不斷演進(jìn)和系統(tǒng)需求日益苛刻,未來的RFIC設(shè)計將更加依賴于先進(jìn)的設(shè)計方法學(xué)、精準(zhǔn)的工藝模型以及芯片-封裝-系統(tǒng)級的協(xié)同優(yōu)化。只有深入理解問題的物理本質(zhì),并靈活運用各種電路技術(shù)和設(shè)計策略,才能設(shè)計出高性能、高可靠性的射頻集成電路,持續(xù)推動無線通信技術(shù)的邊界。